超级透明膜系列

|

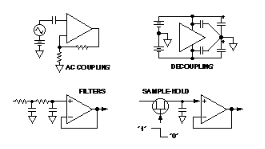

答:为特定应用选择合适的电容器类型并不难。通常,您会发现大多数电容器属于以下四种应用类别之一:

尽管有十几种流行的电容器类型(包括聚乙烯、薄膜、陶瓷、电解等),但您会发现,一般来说,只有一种或两种类型最适合特定应用,因为与其他类型的电容器相关的显著缺陷或对系统性能的“寄生效应”将导致它们被消除。 A.与“理想”电容器不同,“真正的”电容器的典型特征是额外的“寄生”或“非理想”元件或行为,以电阻和电感元件、非线性和介电存储器的形式出现。这些元件产生的特性通常在电容器制造商的数据手册中指定。了解这些寄生效应对每种应用的影响将有助于您选择正确的电容器类型。

A.四种最常见的影响是泄漏(并联电阻)、等效串联电阻 (ESR)、等效串联电感 (ESL) 和介电吸收(存储器)。 电容漏电,RP:漏电是交流耦合应用、存储应用(如模拟积分器和采样保持)以及高阻抗电路中使用电容器时的一个重要参数。

在理想电容器中,电荷Q仅响应外部流动的电流而变化。然而,在实际电容器中,漏电阻允许电荷以由R-C时间常数决定的速率涓涓细流。 电解型电容器(钽和铝)以其高电容而著称,由于隔离电阻差,具有非常高的漏电流(通常约为每μF约5-20 nA),不适合存储或耦合应用。 等效串联电阻,RS:电容器的等效串联电阻(ESR)是电容器引线的电阻与电容器板的等效电阻串联。当高交流电流流动时,ESR会导致电容器耗散功率(从而产生损耗)。这可能会对RF和承载高纹波电流的电源去耦电容产生严重后果,但在精密高阻抗、低电平模拟电路中不太可能产生太大影响。 等效串联电感 (ESL),LS:电容器的等效串联电感(ESL)模拟电容器引线的电感与电容器板的等效电感串联。与ESR一样,ESL在高频(RF)下也可能是一个严重的问题,即使精密电路本身可能在直流或低频下工作。原因是精密模拟电路中使用的晶体管的增益可能扩展到转换频率(Ft)的数百MHz,甚至几GHz,并且可以放大涉及低电感值的谐振。因此,此类电路的电源端子必须在高频下正确去耦。 电解、纸或塑料薄膜电容器是高频去耦的不良选择;它们基本上由两片金属箔组成,由塑料片或纸电介质隔开并形成卷状。这种结构具有相当大的自感,在频率超过几MHz时,其作用更像电感器而不是电容器。 HF去耦更合适的选择是单片陶瓷型电容器,它具有非常低的串联电感。它由金属薄膜和陶瓷电介质的多层夹层组成,薄膜与母线并联连接,而不是串联轧制。 一个小的权衡是,单片陶瓷电容器可以是微音的(即对振动敏感),某些类型甚至可能是自谐振的,具有相对较高的Q值,因为低串联电阻伴随着它们的低电感。另一方面,盘式陶瓷电容器有时具有相当的电感性,尽管价格较低。 答:好问题。由于漏电、ESR和ESL几乎总是难以单独规范,因此许多制造商将漏电、ESR和ESL归为一个称为耗散因数(DF)的单一规格,它基本上描述了电容器的低效率。DF定义为每个周期消耗的能量与每个周期存储的能量之比。实际上,这等于电介质的功率因数或相位角的余弦。如果高频下的耗散主要建模为串联电阻,则在目标临界频率下,等效串联电阻ESR与总容抗之比是DF的良好估计值,

介电吸收,RDA,CDA:单片陶瓷电容器非常适合HF去耦,但它们具有相当大的介电吸收,因此不适合用作采样保持放大器(SHA)的保持电容器。介电吸收是一种类似迟滞的内部电荷分布,它会导致电容器快速放电,然后开路以恢复其部分电荷。由于回收的电荷量是其先前电荷的函数,因此这实际上是一个电荷存储器,并且在使用此类电容器作为保持电容器的任何SHA中都会导致错误。

推荐用于此类应用的电容器包括我们之前谈到的“聚”型电容器,即聚苯乙烯、聚丙烯或特氟龙。这些电容器类型具有非常低的介电吸收(通常为 关于高频去耦的一般注意事项:确保模拟电路在高频和低频下充分去耦的最佳方法是使用电解型电容器,例如钽珠,并与单片陶瓷电容器并联。该组合在低频下将具有高电容,并且在相当高的频率下将保持电容性。通常不需要在每个单独的IC上安装钽电容器,除非在关键情况下;如果每个IC和钽电容器之间的合理宽度PC轨道小于10 cm,则可以在多个IC之间共享一个钽电容器。 关于高频去耦,要记住的另一件事是电容器的实际物理放置。即使是短长的导线也会产生相当大的电感,因此HF去耦电容器应尽可能靠近IC安装,并确保引线由短而宽的PC走线组成。 理想情况下,HF去耦电容应该是表面贴装部件,以消除引线电感,但只要器件引线 mm,引线端电容就可以了。

既然我们已经讨论了电容器作为元件的寄生效应,那么我们来谈谈另一种形式的寄生,称为“杂散”电容。 A.嗯,就像平行板电容器一样,当两个导体彼此靠近时(特别是如果它们并联运行),就会形成杂散电容器,并且不会短路在一起或被用作法拉第屏蔽的导体屏蔽。

杂散或“寄生”电容通常发生在 PC 板上的并行走线之间或 PC 板相对两侧的走线/平面之间。不幸的是,杂散电容的发生和影响 - 特别是在非常高的频率下 - 在电路建模过程中经常被忽视,并且在构建和组装系统电路板时可能导致严重的性能问题;例如,噪声更大,频率响应降低,甚至不稳定。

例如,如果将电容公式应用于电路板相对两侧的走线情况,则对于通用PCB材料(ER= 4.7, d = 1.5 mm),电路板相对两侧导体之间的电容略低于 3 pF/cm2.在 250 MHz 的频率下,3 pF 对应于 212.2 欧姆的电抗! A.您永远无法真正“消除”杂散电容;你能做的最好的事情就是采取措施尽量减少其在电路中的影响。 A.那么,最小化杂散耦合影响的一种方法是使用法拉第屏蔽,它只是耦合源和受影响电路之间的接地导体。 A. 看图;它是一个等效电路,显示如何高频噪声源,VN,通过杂散电容C耦合到系统阻抗Z中。如果我们对 V 几乎没有控制权n或 Z 的位置1,下一个最佳解决方案是插入法拉第盾:

电容耦合的另一个例子是侧面钎焊陶瓷IC封装。这些 DIP 封装有一个小的方形导电 Kovar 盖,焊接在陶瓷封装顶部的金属化边缘上。封装制造商仅提供两种选择:金属化轮辋可以连接到封装的一个角销,也可以不连接。大多数逻辑电路在封装角之一处都有一个接地引脚,因此盖子接地。但许多模拟电路在封装角处没有接地引脚,盖子是浮动的。事实证明,这种电路比塑料DIP封装中的同一芯片更容易受到电场噪声的影响,在塑料DIP封装中,芯片是非屏蔽的。

无论环境噪音水平如何,用户最好将制造商未接地的任何侧面钎焊陶瓷IC的盖子接地。这可以通过将电线焊接到盖子上来完成(这不会损坏设备,因为芯片与盖子进行热和电气隔离)。如果无法焊接到盖子上,可以使用接地的磷青铜夹进行接地连接,或者可以使用导电涂料将盖子连接到接地引脚。切勿在未验证此类盖子实际上未连接的情况下尝试将其接地;确实存在盖子连接到电源轨而不是接地的设备类型! 法拉第屏蔽不切实际的一种情况是在集成电路芯片的键合线之间。这会产生重要后果。两根芯片键合线及其相关引线框架之间的杂散电容约为0.2 pF;观测值通常在 0.05 和 0.6 pF 之间。

考虑连接到高速数据总线的高分辨率转换器ADCDAC)。数据总线的每一条线 V/ns)将能够通过该杂散电容影响转换器的模拟端口;随之而来的数字边沿耦合会降低转换器的性能。

通过隔离数据总线,将锁存缓冲器插入接口,可以避免此问题。虽然该解决方案涉及占用电路板面积、消耗功耗和增加成本的额外组件,但它可以显著改善转换器的信噪比。

(C)于声音线路上是和电感器(L)组成LC网路(NETWORK)用于分频线路-功率放大器(POWERAMPLIFIER)的输出综合信号通过此LC网路时,会依所设 ,提高电子线路的性能和研发新的电路、电子线路及应用领域是电力电子技术领域的科技工作者的一个热门课题。超级 。我的项目之一是对 I2C 温度传感器进行特性描述。在编写一些软件之后,我手工焊接了一个原型设计电路板。由于 。我的项目之一是对 I2C 温度传感器进行特性描述。在编写一些软件之后,我手工焊接了一个原型设计电路板。由于时间仓促,我省去了比较麻烦的去耦 作为一种新型的储能器件,因为其无可替代的优越。 答:为特定应用选择合适的电容器类型并不难。通常,您会发现大多数电容器属于以下四种应用类别之一:

尽管有十几种流行的电容器类型(包括聚乙烯、薄膜、陶瓷、电解等),但您会发现,一般来说,只有一种或两种类型最适合特定应用,因为与其他类型的电容器相关的显著缺陷或对系统性能的“寄生效应”将导致它们被消除。 A.与“理想”电容器不同,“真正的”电容器的典型特征是额外的“寄生”或“非理想”元件或行为,以电阻和电感元件、非线性和介电存储器的形式出现。这些元件产生的特性通常在电容器制造商的数据手册中指定。了解这些寄生效应对每种应用的影响将有助于您选择正确的电容器类型。

A.四种最常见的影响是泄漏(并联电阻)、等效串联电阻 (ESR)、等效串联电感 (ESL) 和介电吸收(存储器)。 电容漏电,RP:漏电是交流耦合应用、存储应用(如模拟积分器和采样保持)以及高阻抗电路中使用电容器时的一个重要参数。

在理想电容器中,电荷Q仅响应外部流动的电流而变化。然而,在实际电容器中,漏电阻允许电荷以由R-C时间常数决定的速率涓涓细流。 电解型电容器(钽和铝)以其高电容而著称,由于隔离电阻差,具有非常高的漏电流(通常约为每μF约5-20 nA),不适合存储或耦合应用。 等效串联电阻,RS:电容器的等效串联电阻(ESR)是电容器引线的电阻与电容器板的等效电阻串联。当高交流电流流动时,ESR会导致电容器耗散功率(从而产生损耗)。这可能会对RF和承载高纹波电流的电源去耦电容产生严重后果,但在精密高阻抗、低电平模拟电路中不太可能产生太大影响。 等效串联电感 (ESL),LS:电容器的等效串联电感(ESL)模拟电容器引线的电感与电容器板的等效电感串联。与ESR一样,ESL在高频(RF)下也可能是一个严重的问题,即使精密电路本身可能在直流或低频下工作。原因是精密模拟电路中使用的晶体管的增益可能扩展到转换频率(Ft)的数百MHz,甚至几GHz,并且可以放大涉及低电感值的谐振。因此,此类电路的电源端子必须在高频下正确去耦。 电解、纸或塑料薄膜电容器是高频去耦的不良选择;它们基本上由两片金属箔组成,由塑料片或纸电介质隔开并形成卷状。这种结构具有相当大的自感,在频率超过几MHz时,其作用更像电感器而不是电容器。 HF去耦更合适的选择是单片陶瓷型电容器,它具有非常低的串联电感。它由金属薄膜和陶瓷电介质的多层夹层组成,薄膜与母线并联连接,而不是串联轧制。 一个小的权衡是,单片陶瓷电容器可以是微音的(即对振动敏感),某些类型甚至可能是自谐振的,具有相对较高的Q值,因为低串联电阻伴随着它们的低电感。另一方面,盘式陶瓷电容器有时具有相当的电感性,尽管价格较低。 答:好问题。由于漏电、ESR和ESL几乎总是难以单独规范,因此许多制造商将漏电、ESR和ESL归为一个称为耗散因数(DF)的单一规格,它基本上描述了电容器的低效率。DF定义为每个周期消耗的能量与每个周期存储的能量之比。实际上,这等于电介质的功率因数或相位角的余弦。如果高频下的耗散主要建模为串联电阻,则在目标临界频率下,等效串联电阻ESR与总容抗之比是DF的良好估计值,

介电吸收,RDA,CDA:单片陶瓷电容器非常适合HF去耦,但它们具有相当大的介电吸收,因此不适合用作采样保持放大器(SHA)的保持电容器。介电吸收是一种类似迟滞的内部电荷分布,它会导致电容器快速放电,然后开路以恢复其部分电荷。由于回收的电荷量是其先前电荷的函数,因此这实际上是一个电荷存储器,并且在使用此类电容器作为保持电容器的任何SHA中都会导致错误。

推荐用于此类应用的电容器包括我们之前谈到的“聚”型电容器,即聚苯乙烯、聚丙烯或特氟龙。这些电容器类型具有非常低的介电吸收(通常为 关于高频去耦的一般注意事项:确保模拟电路在高频和低频下充分去耦的最佳方法是使用电解型电容器,例如钽珠,并与单片陶瓷电容器并联。该组合在低频下将具有高电容,并且在相当高的频率下将保持电容性。通常不需要在每个单独的IC上安装钽电容器,除非在关键情况下;如果每个IC和钽电容器之间的合理宽度PC轨道小于10 cm,则可以在多个IC之间共享一个钽电容器。 关于高频去耦,要记住的另一件事是电容器的实际物理放置。即使是短长的导线也会产生相当大的电感,因此HF去耦电容器应尽可能靠近IC安装,并确保引线由短而宽的PC走线组成。 理想情况下,HF去耦电容应该是表面贴装部件,以消除引线电感,但只要器件引线 mm,引线端电容就可以了。

既然我们已经讨论了电容器作为元件的寄生效应,那么我们来谈谈另一种形式的寄生,称为“杂散”电容。 A.嗯,就像平行板电容器一样,当两个导体彼此靠近时(特别是如果它们并联运行),就会形成杂散电容器,并且不会短路在一起或被用作法拉第屏蔽的导体屏蔽。

杂散或“寄生”电容通常发生在 PC 板上的并行走线之间或 PC 板相对两侧的走线/平面之间。不幸的是,杂散电容的发生和影响 - 特别是在非常高的频率下 - 在电路建模过程中经常被忽视,并且在构建和组装系统电路板时可能导致严重的性能问题;例如,噪声更大,频率响应降低,甚至不稳定。

例如,如果将电容公式应用于电路板相对两侧的走线情况,则对于通用PCB材料(ER= 4.7, d = 1.5 mm),电路板相对两侧导体之间的电容略低于 3 pF/cm2.在 250 MHz 的频率下,3 pF 对应于 212.2 欧姆的电抗! A.您永远无法真正“消除”杂散电容;你能做的最好的事情就是采取措施尽量减少其在电路中的影响。 A.那么,最小化杂散耦合影响的一种方法是使用法拉第屏蔽,它只是耦合源和受影响电路之间的接地导体。 A. 看图;它是一个等效电路,显示如何高频噪声源,VN,通过杂散电容C耦合到系统阻抗Z中。如果我们对 V 几乎没有控制权n或 Z 的位置1,下一个最佳解决方案是插入法拉第盾:

电容耦合的另一个例子是侧面钎焊陶瓷IC封装。这些 DIP 封装有一个小的方形导电 Kovar 盖,焊接在陶瓷封装顶部的金属化边缘上。封装制造商仅提供两种选择:金属化轮辋可以连接到封装的一个角销,也可以不连接。大多数逻辑电路在封装角之一处都有一个接地引脚,因此盖子接地。但许多模拟电路在封装角处没有接地引脚,盖子是浮动的。事实证明,这种电路比塑料DIP封装中的同一芯片更容易受到电场噪声的影响,在塑料DIP封装中,芯片是非屏蔽的。

无论环境噪音水平如何,用户最好将制造商未接地的任何侧面钎焊陶瓷IC的盖子接地。这可以通过将电线焊接到盖子上来完成(这不会损坏设备,因为芯片与盖子进行热和电气隔离)。如果无法焊接到盖子上,可以使用接地的磷青铜夹进行接地连接,或者可以使用导电涂料将盖子连接到接地引脚。切勿在未验证此类盖子实际上未连接的情况下尝试将其接地;确实存在盖子连接到电源轨而不是接地的设备类型! 法拉第屏蔽不切实际的一种情况是在集成电路芯片的键合线之间。这会产生重要后果。两根芯片键合线及其相关引线框架之间的杂散电容约为0.2 pF;观测值通常在 0.05 和 0.6 pF 之间。

考虑连接到高速数据总线的高分辨率转换器ADCDAC)。数据总线的每一条线 V/ns)将能够通过该杂散电容影响转换器的模拟端口;随之而来的数字边沿耦合会降低转换器的性能。

通过隔离数据总线,将锁存缓冲器插入接口,可以避免此问题。虽然该解决方案涉及占用电路板面积、消耗功耗和增加成本的额外组件,但它可以显著改善转换器的信噪比。

(C)于声音线路上是和电感器(L)组成LC网路(NETWORK)用于分频线路-功率放大器(POWERAMPLIFIER)的输出综合信号通过此LC网路时,会依所设 ,提高电子线路的性能和研发新的电路、电子线路及应用领域是电力电子技术领域的科技工作者的一个热门课题。超级 。我的项目之一是对 I2C 温度传感器进行特性描述。在编写一些软件之后,我手工焊接了一个原型设计电路板。由于 。我的项目之一是对 I2C 温度传感器进行特性描述。在编写一些软件之后,我手工焊接了一个原型设计电路板。由于时间仓促,我省去了比较麻烦的去耦 作为一种新型的储能器件,因为其无可替代的优越。 |